強磁性体は、熱という外部因子で強磁性と常磁性を制御することができます。強磁性半導体電界効果型トランジスタ(FET)では、外部因子とし電圧で強磁性・常磁性を制御することができます。これは、温度一定の状態でも、FETのゲートに加えた電圧で転移温度を変化させていることになります。

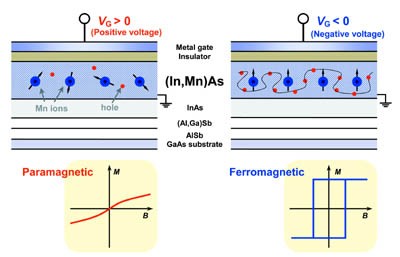

強磁性半導体FETの構造は、GaAs基板上にスペーサーをはさんで強磁性半導体となるインジウムマンガンヒ素(In,Mn)Asを結晶成長します。(In,Mn)AsはMnがホールを放出するp型半導体です。ホール濃度が大きいほど、転移温度は高くなります。(In,Mn)Asの上に絶縁膜となるSiO2をはさんでゲートをつけます。このFET構造で低温においては、ゲートにマイナスの電圧を加えると、(In,Mn)Asのホール濃度が大きくなり強磁性となり、プラスの電圧を加えると、(In,Mn)Asのホール濃度が小さくなり常磁性となります。

実際に強磁性半導体FETができるまでの行程は、スーパークリーンルームの中での作業と実験室での作業に分かれます。これらの概要は下のようになります。

強磁性半導体FETの構造は、GaAs基板上にスペーサーをはさんで強磁性半導体となるインジウムマンガンヒ素(In,Mn)Asを結晶成長します。(In,Mn)AsはMnがホールを放出するp型半導体です。ホール濃度が大きいほど、転移温度は高くなります。(In,Mn)Asの上に絶縁膜となるSiO2をはさんでゲートをつけます。このFET構造で低温においては、ゲートにマイナスの電圧を加えると、(In,Mn)Asのホール濃度が大きくなり強磁性となり、プラスの電圧を加えると、(In,Mn)Asのホール濃度が小さくなり常磁性となります。

| (In,Mn)As FET構造における電界制御強磁性の概念図 | |

|

ゲート電圧Vgがマイナスのときは、強磁性半導体のホール濃度が大きくなり強磁性(Ferromagnetic)となります。逆に、ゲート電圧Vgがプラスのときは常磁性(Paramagnetic)となります。下側のグラフにおいて、B は外部磁場、M は磁化です。強磁性のときは図のようなヒステリシスループと呼ばれるものが観測されます。

|

実際に強磁性半導体FETができるまでの行程は、スーパークリーンルームの中での作業と実験室での作業に分かれます。これらの概要は下のようになります。

|

| ||||||||||||||||||

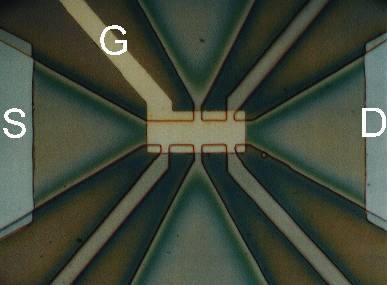

測定は、ホールバー(右図)のソース(S)-ドレイン(D)間の面方向に電流を流し、面直に磁場を加えたときのホール抵抗とシート抵抗(面抵抗)の磁場依存性を測定します。その際、ゲート(G)にプラスとマイナスの電圧を加えてキャリヤ濃度を変化させた場合の特性も測定します。下図に測定から得られた結果を説明します。

測定は、ホールバー(右図)のソース(S)-ドレイン(D)間の面方向に電流を流し、面直に磁場を加えたときのホール抵抗とシート抵抗(面抵抗)の磁場依存性を測定します。その際、ゲート(G)にプラスとマイナスの電圧を加えてキャリヤ濃度を変化させた場合の特性も測定します。下図に測定から得られた結果を説明します。

| (In,Mn)As FET構造の磁気特性 | |

|

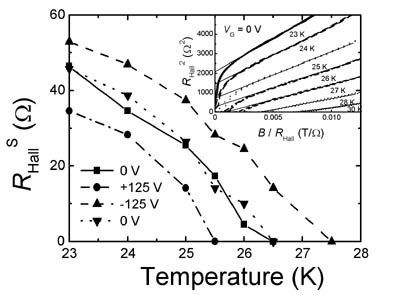

異なるゲート電圧時のホール抵抗(RHall)と磁場(B)の関係

22.5Kにおいて、ゲート電圧が+125V、0V、-125Vのときのホール抵抗の磁場依存性の測定結果です。プラスのゲート電圧によりキャリヤを減らすことで(In,Mn)Asの強磁性的秩序が消え常磁性になり、マイナスのゲート電圧により強磁性的秩序がより強く誘起されます。強磁性的秩序が強くなるにつれクリアーなヒステリシスループが観測されます。 |

|

異なるゲート電圧時のホール抵抗(RHall)の温度依存性

ホール抵抗(RHall)が0となるときの、ゲート電圧が+125Vと-125Vの間の範囲が、電界により強磁性-常磁性状態間のスイッチが可能な領域となります。転移温度の変化量はだいたい25.5Kから27.5Kまでの約2Kとなります。よって、ゲート電圧が0Vの状態から転移温度を約±1K変化させることができます。 |

今後の強磁性半導体FETの研究には、強磁性-常磁性状態間スイッチが観測できる温度領域を広げる、(Ga,Mn)Asで強磁性-常磁性状態間スイッチを観測する、低電圧動作が可能な構造の考案、微細加工技術を用いた構造、他の物理現象との融合などがあげられます。

これらの研究は低温での観測が中心であるが、室温動作を目標に、強磁性金属では実現できないデバイスに発展していくことを期待しています。

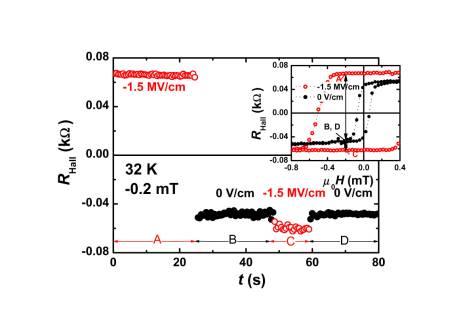

電界アシスト磁化反転

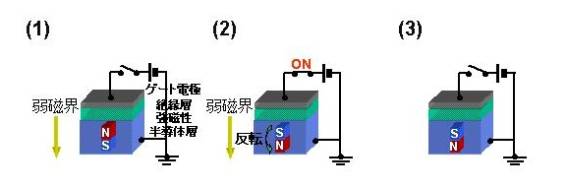

(In,Mn)Asをチャネル層にもった電界効果型トランジスタ構造においては、ゲート電界で等温可逆的に強磁性-常磁性状態間のスイッチングができるだけでなく、保磁力(磁化反転に必要な磁界)も変化させることができます。このことを利用すると磁化反転させる時にゲート電界で保磁力を小さくすれば、小さな磁界で磁化反転をさせることができます。現在の磁気メモリデバイスでは外部磁界を印加することで磁化を反転し、書き込みが行われています。しかし素子サイズの減少とともに磁化反転に必要な外部磁界が増加し、その磁界を発生するために必要な電流が増大するという問題が生じています。電界アシスト磁化反転は、磁化反転に必要な磁界をゲート電界で小さくすることができるため、書き込みに必要な磁界、またそれを発生するために必要な電流を減らすことができると期待されます。(In,Mn)As FET構造における電界アシスト磁化反転

電界アシスト磁化反転の模式図

(2) ゲート電界によって保磁力を小さくすると弱磁界で磁化反転する。

(3) ゲート電界をオフし磁界をゼロに戻しても磁化の方向は安定(磁化反転終了)。

実験結果

今後の強磁性半導体FET構造の研究目標として

●強磁性-常磁性状態間スイッチが観測できる温度領域を広げる

●(Ga,Mn)Asで強磁性-常磁性状態間スイッチを観測する

●低電圧動作が可能な構造の考案

●他の物理現象との融合 を考えています。

現在のところ低温での実験が中心ですが、室温動作を目標に、強磁性金属では実現できないデバイスに発展していくことを期待しています。

もどる